# INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC17 1998 Oct 07

| 1    | FEATURES                                                 |

|------|----------------------------------------------------------|

| 2    | ORDERING INFORMATION                                     |

| 3    | GENERAL DESCRIPTION                                      |

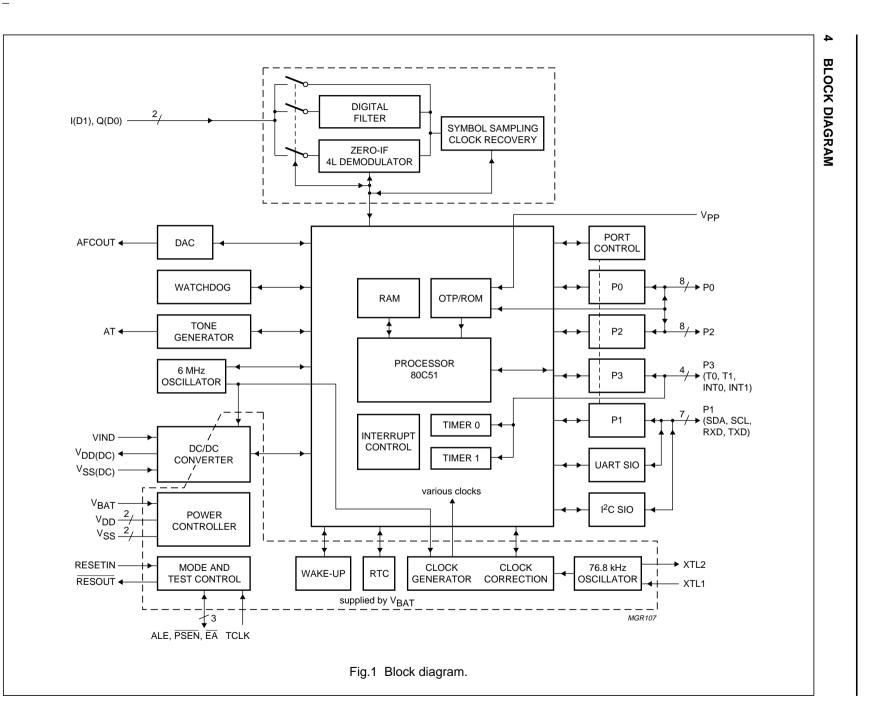

| 4    | BLOCK DIAGRAM                                            |

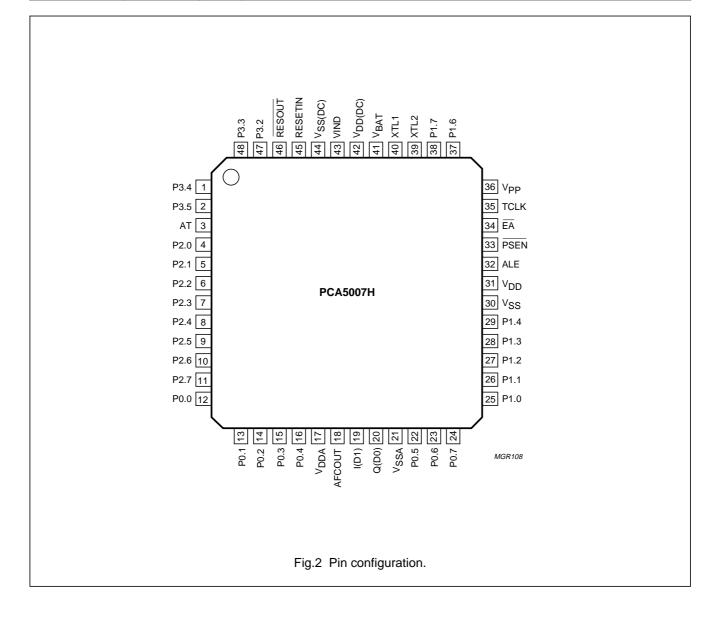

| 5    | PINNING                                                  |

| 6    | FUNCTIONAL DESCRIPTION                                   |

| 6.1  | General                                                  |

| 6.2  | CPU timing                                               |

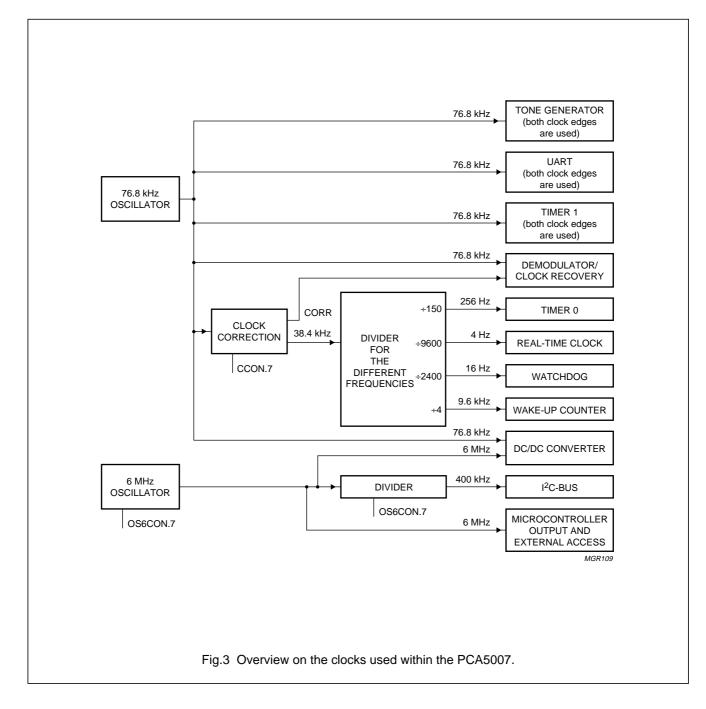

| 6.3  | Overview on the different clocks used within the PCA5007 |

| 6.4  | Memory organization                                      |

| 6.5  | Addressing                                               |

| 6.6  | I/O facilities                                           |

| 6.7  | Timer/event counters                                     |

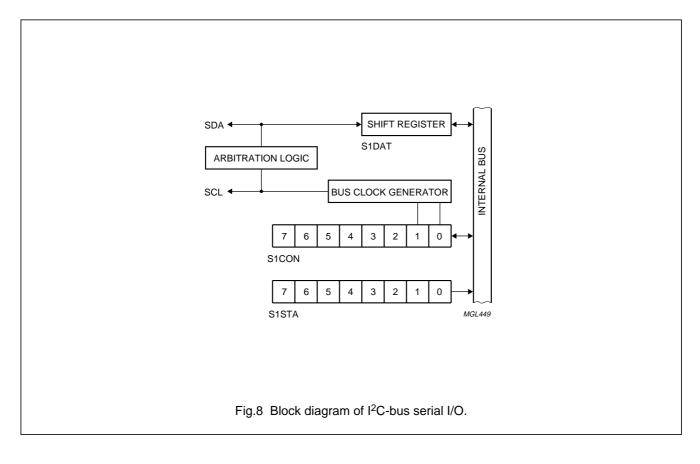

| 6.8  | I <sup>2</sup> C-bus serial I/O                          |

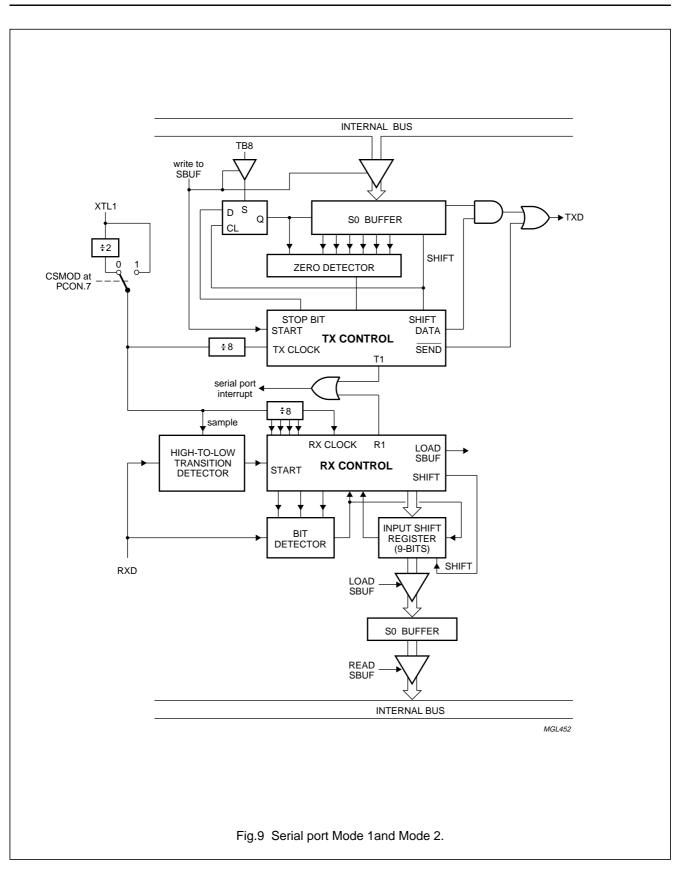

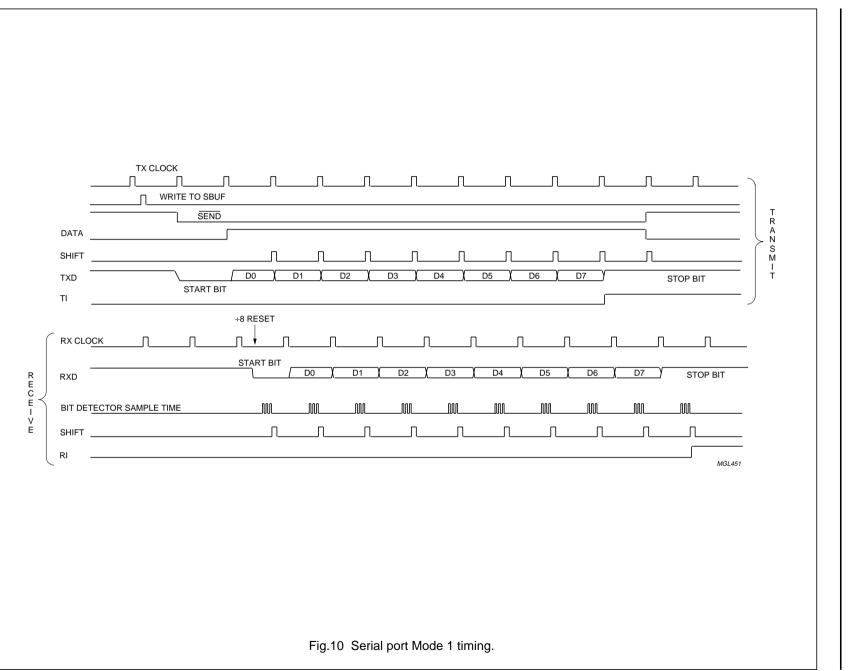

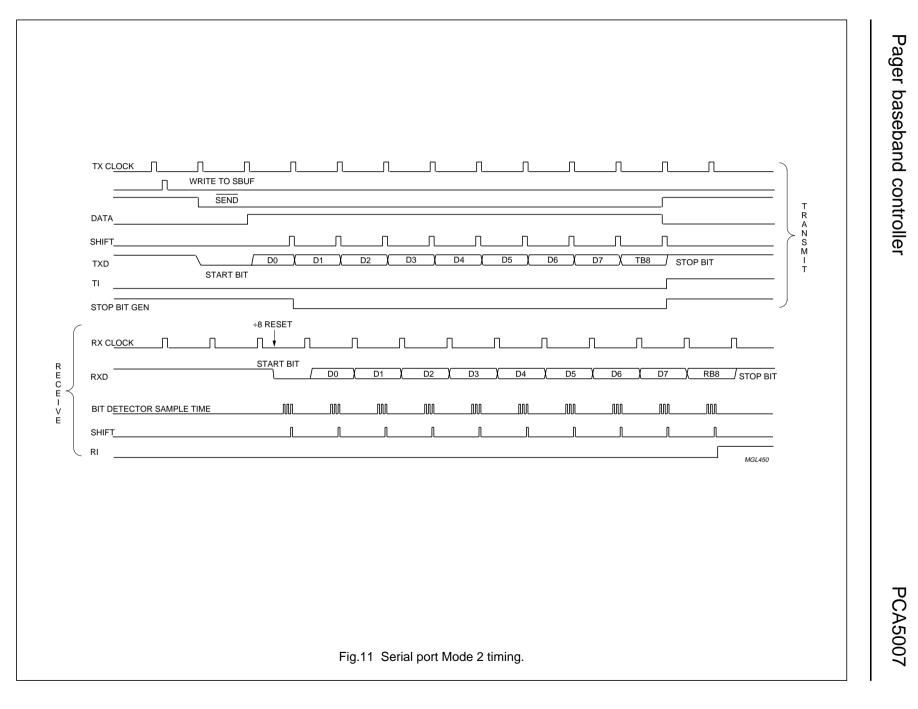

| 6.9  | Serial interface SIO0: UART                              |

| 6.10 | 76.8 kHz oscillator                                      |

| 6.11 | Clock correction                                         |

| 6.12 | 6 MHz oscillator                                         |

| 6.13 | Real-time clock                                          |

| 6.14 | Wake-up counter                                          |

| 6.15 | Tone generator                                           |

| 6.16 | Watchdog timer                                           |

| 6.17 | 2 or 4-FSK demodulator, filter and clock                 |

|      | recovery circuit                                         |

| 6.18 | AFC-DAC                                                  |

| 6.19 | Interrupt system                                         |

| 6.20 | Idle and power-down operation                            |

| 6.21 | Reset                                                    |

| 6.22 | DC/DC converter                                          |

| 7    | INSTRUCTION SET                                          |

| 7.1  | Instruction Map                                          |

| 8    | LIMITING VALUES                                          |

| 9    | EXTERNAL COMPONENTS                                      |

| 10   | DC CHARACTERISTICS                                       |

- 11 AC CHARACTERISTICS

- 12 CHARACTERISTIC CURVES

- 13 TEST AND APPLICATION INFORMATION

# PCA5007

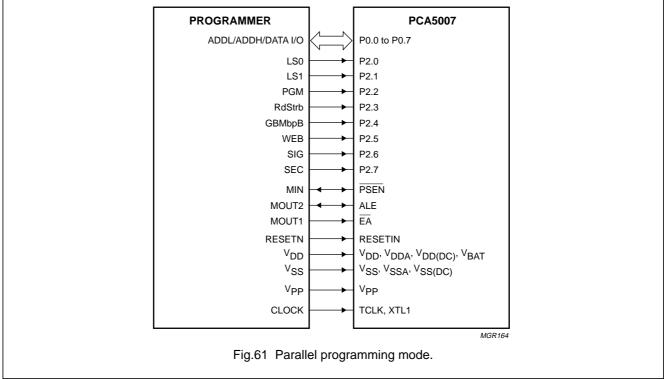

| 14                                                                            | APPENDIX 1: SPECIAL MODES OF THE<br>PCA5007                                                                                                                                                                                    |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14.1<br>14.2<br>14.3                                                          | Overview<br>OTP parallel programming mode<br>Test modes                                                                                                                                                                        |

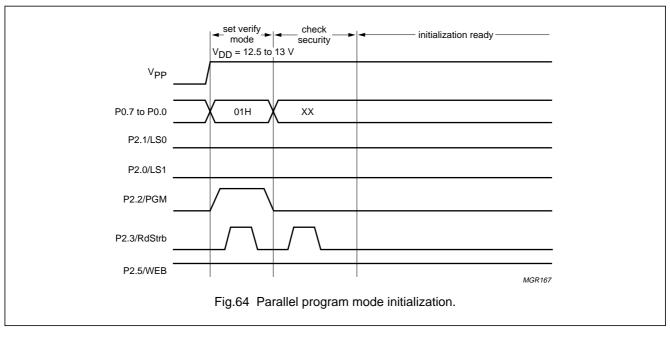

| 15                                                                            | APPENDIX 2: THE PARALLEL<br>PROGRAMMING MODE                                                                                                                                                                                   |

| 15.1<br>15.2<br>15.3<br>15.4<br>15.5<br>15.6<br>15.7<br>15.8<br>15.9<br>15.10 | Introduction<br>General description<br>Entering the parallel programming mode<br>Address space<br>Single byte programming<br>Multiple byte programming<br>High voltage timing<br>OTP test modes<br>Signature bytes<br>Security |

| 16                                                                            | APPENDIX 3: OS SHEET                                                                                                                                                                                                           |

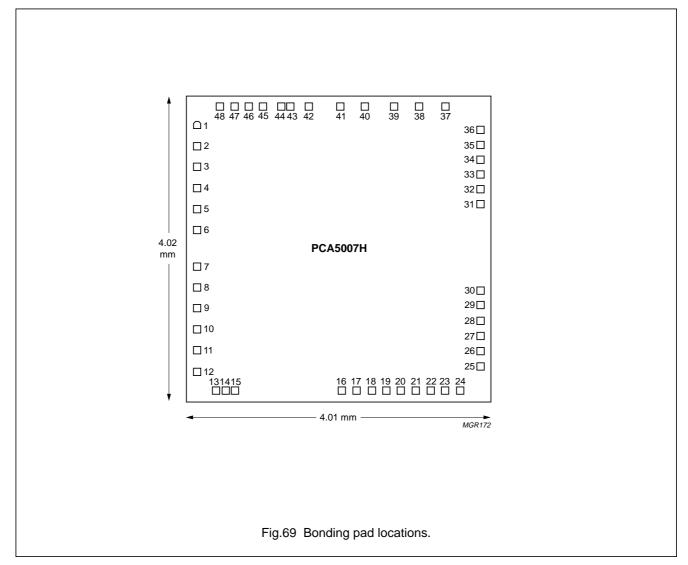

| 17                                                                            | APPENDIX 4: BONDING PAD LOCATIONS                                                                                                                                                                                              |

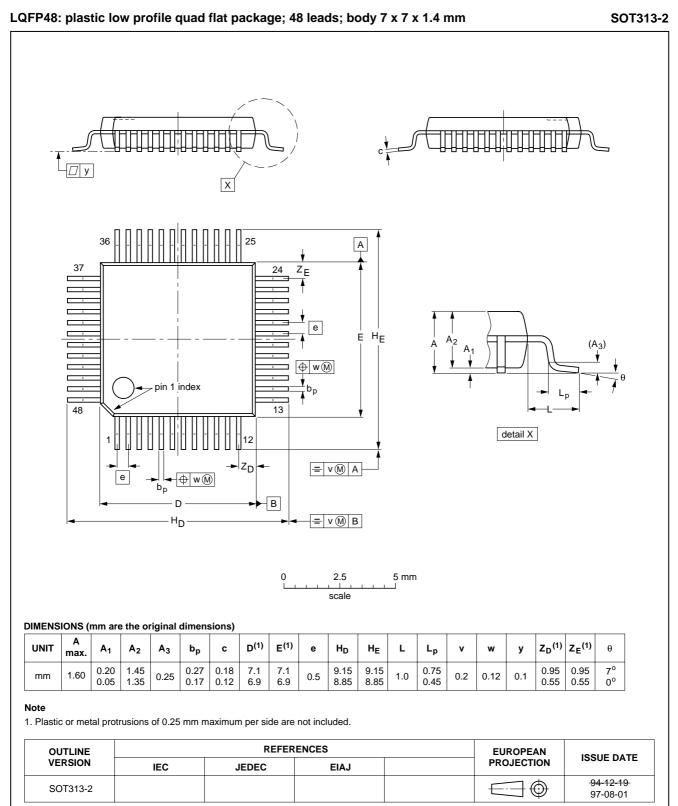

| 18                                                                            | PACKAGE OUTLINE                                                                                                                                                                                                                |

| 19                                                                            | SOLDERING                                                                                                                                                                                                                      |

| 19.1<br>19.2<br>19.3<br>19.4<br>20<br>21<br>22                                | Introduction<br>Reflow soldering<br>Wave soldering<br>Repairing soldered joints<br>DEFINITIONS<br>LIFE SUPPORT APPLICATIONS<br>PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS                                                 |

|                                                                               |                                                                                                                                                                                                                                |

# PCA5007

### **1 FEATURES**

- Operating temperature from: -10 to +55 °C

- Supply voltage range with on-chip DC/DC converter: 0.9 to 1.6 V

- · Low operating and standby current consumption

- On-chip DC/DC converter generates the supply voltage for the PCA5007 and external circuitry from a single cell battery

- Battery low detector

- Low electromagnetic noise emission

- Full static asynchronous 80C51 CPU (8-bit CPU)

- Recovery from lowest power standby Idle mode to full speed operation within microseconds

- 20 kbytes of One-Time Programmable (OTP) memory and 1-kbyte of RAM on-chip

- 27 general purpose I/O port lines (4 ports with interrupt possibility)

- 15 different interrupt sources with selectable priority

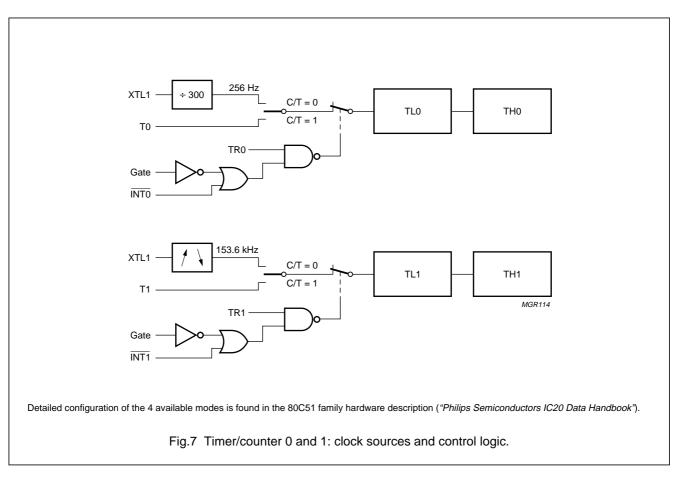

- 2 standard timer/event counters T0 and T1

- I<sup>2</sup>C-bus serial port (single 100 kHz master transmitter and receiver)

- Subset of standard UART serial port (8 and 9-bit transmission at 4800/9600 bits/s)

- 76.8 kHz crystal oscillator reference with digital clock correction for real time and paging protocol

- Real-Time Clock (RTC)

- Receiver and synthesizer control

- Receiver control by software through general purpose I/Os

- Synthesizer control by software through general purpose I/Os

- 6-bit DAC for AFC to the receiver local oscillator

- Dedicated protocol timer.

### 2 ORDERING INFORMATION

| TYPE                  | PRODUCT TYPE       |        |                                                                                  |          |

|-----------------------|--------------------|--------|----------------------------------------------------------------------------------|----------|

| NUMBER <sup>(1)</sup> | PRODUCT TIPE       | NAME   | DESCRIPTION                                                                      | VERSION  |

| PCA5007H/XXX          | pre-programmed OTP | LQFP48 | plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4$ mm | SOT313-2 |

### Note

1. Please refer to the Order Entry Form (OEF) for this device for the full type number to use when ordering. This type number will also specify the required OTP code.

- Decoding of paging data

- POCSAG or APOC phase 1, advanced high speed paging protocols are also supported

- Supported data rates: 1200, 1600, 2400 and 3200 symbols/s using a 76.8 kHz crystal oscillator

- Demodulation of Zero-IF I and Q 4 or 2 level FSK input or direct data input

- Noise filtering of data input and symbol clock reconstruction

- De-interleaving, error checking and correction, sync word detection address recognition, buffering and more is done in software

- All user functions (keypad interface, alerter control, display, etc.) are implemented in software.

- Musical tone generator for beeper, controlled by the microcontroller

- Watchdog timer

- 48-pin LQFP package.

# PCA5007

### **3 GENERAL DESCRIPTION**

The PCA5007 pager baseband controller is manufactured in an advanced CMOS/OTP technology.

The PCA5007 is an 8-bit microcontroller especially suited for pagers. For this purpose, features such as a 4 or 2 level FSK demodulator, filter, clock recovery, protocol timer, DC/DC converter optimized for small paging systems and RTC are integrated on-chip.

The device is optimized for low power consumption. The PCA5007 has several software selectable modes for power reduction: Idle and power-down mode of the microcontroller, and standby and off mode of the DC/DC converter. The instruction set of the PCA5007 is based on that of the 80C51. The PCA5007 also functions as an arithmetic processor having facilities for both binary and BCD arithmetic plus bit-handling capabilities. The instruction set consists of over 100 instructions: 49 one-byte, 46 two-byte, and 16 three-byte.

This data sheet details the properties of the PCA5007. For details of the l<sup>2</sup>C-bus functions see "*The l<sup>2</sup>C-bus and how to use it*". For details on the basic 80C51 properties and features see "*Data Handbook IC20*".

Philips Semiconductors

# Pager baseband controller

# PCA5007

1998 Oct 07

сл

Product specification

PCA5007

### 5 PINNING

| SYMBOL           | PIN      | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.4 and P3.5    | 1 and 2  | I/O  | <b>Port 3:</b> P3.4 and P3.5 are configured as push-pull output only (option 3R; see Section 6.6). Using the software input commands or the secondary port function is possible by driving the port 3 output lines accordingly:                                                                                                                                                                                                                                                                                                 |

|                  |          |      | P3.4 secondary function: T0 (counter input for T0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                  |          |      | P3.5 secondary function: T1 (counter input for T1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AT               | 3        | 0    | Beeper high volume control output. Used to drive external bipolar transistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

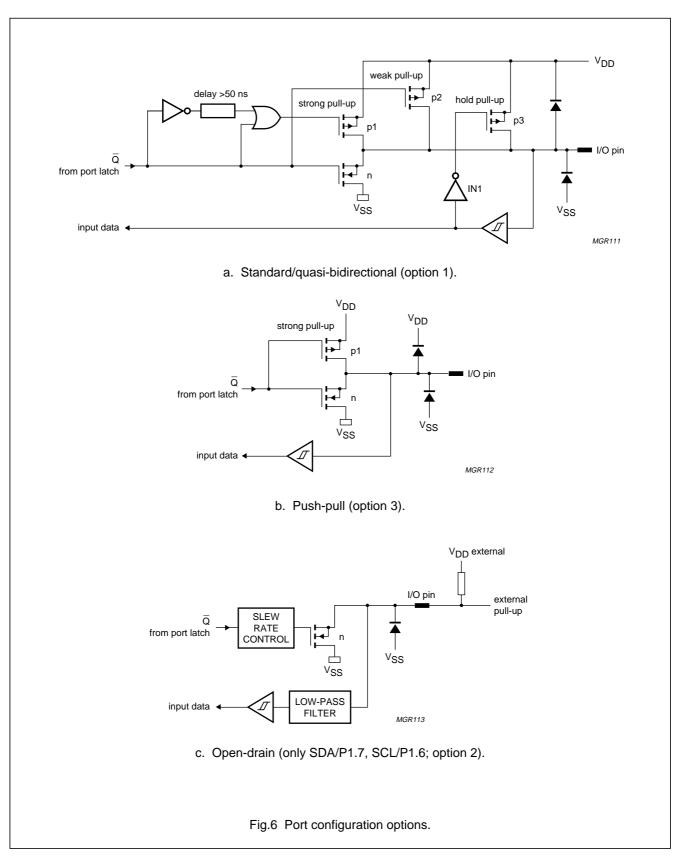

| P2.0 to P2.7     | 4 to 11  | I/O  | <b>Port 2:</b> Port 2 is an 8-bit bidirectional I/O port with internal pull-ups (option 1S; see Section 6.6.3). As inputs, port 2 pins that are externally pulled LOW will source current because of the internal pull-ups. (see Chapter "DC characteristics": $I_{pu}$ ). Port 2 emits the high-order address byte during fetches from external program memory. In this application, it uses strong internal pull-ups when emitting logic 1s. Port 2 is also used to control the parallel programming mode of the on-chip OTP. |

| P0.0 to P0.4     | 12 to 16 | I/O  | <b>Port 0:</b> Port 0 is a bidirectional I/O port with internal pull-ups (option 1S; see Section 6.6.3). Port 0 pins that have logic 1s written to them are pulled HIGH by the internal pull-ups and can be used as inputs. Port 0 is also the multiplexed low-order address and data bus during access to external program and data memory. In this application, it uses strong internal pull-ups when emitting 1s. Port 0 also outputs the code bytes during OTP programming verification.                                    |

| V <sub>DDA</sub> | 17       | S    | supply voltage for the analog parts of the PCA5007 and the receiver/synthesizer control signals (Port 0 pins)                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AFCOUT           | 18       | 0    | Buffered analog output of DAC for automatic receiver frequency control.<br>A voltage proportional to the offset of the receiver frequency can be generated.<br>Can be enabled/disabled by software.                                                                                                                                                                                                                                                                                                                             |

| I(D1)            | 19       | I    | input from receiver: may be demodulated NRZ signal or Zero-IF. In phase limited signal                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Q(D0)            | 20       | I    | input from receiver: may be demodulated NRZ signal or Zero-IF, Quadrature limited signal.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>SSA</sub> | 21       | S    | ground signal reference (for the analog parts) (connected to substrate)                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P0.5 to P0.7     | 22 to 24 | I/O  | <b>Port 0:</b> Port 0 is a bidirectional I/O port with internal pull-ups (option 1R,1R and 1S; see Section 6.6.3). Port 0 pins that have logic 1s written to them are pulled HIGH by the internal pull-ups and can be used as inputs. Port 0 is also the multiplexed low-order address and data bus during access to external program and data memory. In this application, it uses strong internal pull-ups when emitting 1s. Port 0 also outputs the code bytes during OTP programming verification.                          |

| P1.0 to P1.2     | 25 to 27 | I/O  | <b>Port 1:</b> Port 1 is an 8-bit quasi bidirectional I/O port with internal pull-ups.<br>Port 1 pins that have logic 1s written to them are pulled HIGH by the internal pull-ups and can be used as inputs. As inputs, port 1 pins that are externally pulled LOW will source current because of the internal pull-ups (see Chapter "DC characteristics": I <sub>pu</sub> ). P1.0 to P1.2 have external interrupts INT2 to INT4 assigned.                                                                                      |

| P1.3             | 28       | I/O  | If the UART is disabled (ENS1 in S1CON.4 = 0) then P1.3 can be used as general purpose P1 port pin. If the UART function is required, then a logic 1 must be written to P1.3. This I/O then becomes the RXD/data line of the UART.                                                                                                                                                                                                                                                                                              |

PCA5007

| SYMBOL              | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1.4                | 29  | I/O  | If the UART is disabled (ENS1 in S1CON.4 = 0) then P1.4 can be used as general purpose P1 port pin. If the UART function is required, then a logic 1 must be written to P1.4. This I/O then becomes the TXD/clock line of the UART. P1.4 has external interrupt INT6 (X6) assigned.                                                                                               |

| V <sub>SS</sub>     | 30  | S    | ground (connected to substrate)                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>DD</sub>     | 31  | S    | supply voltage for the core logic and most peripheral drivers of the PCA5007 (see $V_{\text{DDA}})$                                                                                                                                                                                                                                                                               |

| ALE                 | 32  | I/O  | Address Latch Enable: output pulse for latching the low byte of the address during an access to external memory.                                                                                                                                                                                                                                                                  |

| PSEN                | 33  | I/O  | <b>Program Store Enable:</b> the read strobe to external program memory. When the device is executing code from the external program memory, <b>PSEN</b> is activated for each code byte fetch.                                                                                                                                                                                   |

| ĒĀ                  | 34  | I/O  | <b>External Access Enable:</b> $\overline{EA}$ must be externally held LOW to enable the device to fetch code from external program memory locations 0000H to 4FFFH. If $\overline{EA}$ is held HIGH, the device executes from internal program memory unless the program counter contains an address greater the 4FFFH (20 kbytes).                                              |

| TCLK                | 35  | I    | clock input for use as timing reference in external access mode and emulation                                                                                                                                                                                                                                                                                                     |

| V <sub>PP</sub>     | 36  | S    | Programming voltage (12.5 V) for the OTP. Is connected to $V_{\mbox{SS}}$ in the application.                                                                                                                                                                                                                                                                                     |

| P1.6(SCL)           | 37  | I/O  | If the I <sup>2</sup> C-bus is disabled (ENS1 in S1CON.6 = 0) then P1.6 can be used as general purpose P1 port pin. If the I <sup>2</sup> C-bus function is required, then a logic 1 must be written to P1.6. This I/O then becomes the clock line of the I <sup>2</sup> C-bus. P1.6 is equipped with an open-drain output buffer. The pin has no clamp diode to $V_{DD}$ .       |

| P1.7(SDA)           | 38  | I/O  | If the I <sup>2</sup> C-bus is disabled (ENS1 in S1CON.6 = 0) then P1.7 can be used as general purpose P1 port pin. If the I <sup>2</sup> C-bus function is required, then a logic 1 must be written to P1.7. This I/O then becomes the data line of the I <sup>2</sup> C-bus. P1.7 is equipped with an open-drain output buffer. The pin has no clamp diode to V <sub>DD</sub> . |

| XTL2                | 39  | 0    | output from the current source oscillator amplifier                                                                                                                                                                                                                                                                                                                               |

| XTL1                | 40  | I    | input to the inverting oscillator amplifier and time reference for pager decoder, real-time clock and timers                                                                                                                                                                                                                                                                      |

| V <sub>BAT</sub>    | 41  | S    | Supply terminal from battery. Is used for supplying parts of the chip that need to operate at all times.                                                                                                                                                                                                                                                                          |

| V <sub>DD(DC)</sub> | 42  | 0    | Supply voltage output of the DC/DC converter. An external capacitor is required.                                                                                                                                                                                                                                                                                                  |

| VIND                | 43  | I    | Current input for the DC/DC converter. The booster inductor needs to be connected externally.                                                                                                                                                                                                                                                                                     |

| V <sub>SS(DC)</sub> | 44  | S    | ground (connected to substrate) OTP                                                                                                                                                                                                                                                                                                                                               |

| RESETIN             | 45  | I    | Schmitt trigger reset input for the PCA5007. External R and C need to be connected to the battery supply. All internal storage elements (except microcontroller RAM) are initialized when this input is activated.                                                                                                                                                                |

PCA5007

| SYMBOL       | PIN       | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                              |

|--------------|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESOUT       | 46        | 0    | Monitor output for the emulation system. Is active (LOW) whenever a reset is applied to the microcontroller. (a reset can be forced by RESETIN, watchdog or wake-up from DC/DC converter in off mode). A reset to the microcontroller initializes all SFRs and port pins; it has no impact on the blocks operating from $V_{BAT}$ .                                      |

| P3.2 to P3.3 | 47 and 48 | I/O  | <ul> <li>Port 3: P3.2 and P3.3 are configured as push-pull output only (option 3R; see Section 6.6). Using the software input commands or the secondary port function is possible by driving the port 3 output lines accordingly:</li> <li>P3.2 secondary function: INT0 (external interrupt 0)</li> <li>P3.3 secondary function: INT1 (external interrupt 1)</li> </ul> |

# PCA5007

### **6 FUNCTIONAL DESCRIPTION**

### 6.1 General

The PCA5007 contains a high-performance CMOS microcontroller and the required peripheral circuitry to implement high-speed pagers for the modern paging protocols. For this purpose, features such as FSK demodulator, protocol timer, real-time clock and DC/DC converter have been integrated on-chip.

The microcontroller embedded within the PCA5007 implements the standard 80C51 architecture and supports the complete instruction set of the 80C51 with all addressing modes.

The PCA5007 contains 20 kbytes of OTP program memory; 1-kbyte of static read/write data memory, 27 I/O lines, two 16-bit timer/event counters, a fifteen-source two priority-level, nested interrupt structure and on-chip oscillator and timing circuit.

The PCA5007 devices have several software selectable modes of reduced activity for power reduction; Idle for the CPU and standby or off for the DC/DC converter. The Idle mode freezes the CPU while allowing the RAM, timers, serial I/O and interrupt system to continue functioning. The standby mode for the DC/DC converter allows a high efficiency of the latter at low currents and the off mode reduces the supply voltage to the battery level. In the off mode the RAM contents are preserved, the real-time clock and protocol timer are operating, but all other chip functions are inoperative.

Two serial interfaces are provided on-chip; a UART serial interface and an  $I^2$ C-bus serial interface. The  $I^2$ C-bus serial interface has byte oriented master functions allowing communication with a whole family of  $I^2$ C-bus compatible slave devices.

### 6.2 CPU timing

The internal CPU timing of the PCA5007 is completely different to other implementations of this core. The CPU is realized in asynchronous handshaking technology, which results in extremely low power consumption and low EMC noise generation.

### 6.2.1 BASICS

The implementation of the CPU of the PCA5007 as a block in handshake technology has become possible through the TANGRAM tool set, developed in the Philips Natlab in Eindhoven. TANGRAM is a high level programming language which allows the description of parallel and sequential processes that can be compiled into logic on silicon. The CPU has the following features:

- No clock is needed. Every function within the CPU is self timed and always runs at the maximum speed that a given silicon die under the current operating conditions (supply voltage and temperature) allows.

- The CPU fetches opcodes with maximum speed until a special mode (e.g. Idle) is entered that stops this sequence.

- Only bytes that are required are fetched from the program memory. The dummy read cycles which exist in the standard 80C51 have been omitted to save power.

- To further speed up the execution of a program, the next sequential byte is always fetched from the code memory during the execution of the current command. In the event of jumps the prefetched byte is discarded.

- Since no clocks are required, the operating power consumption is essentially lower compared to conventional architectures and Idle power consumption is reduced to nearly zero (leakage only).

- Clocks are only required as timing references for timers/counters and for generating the timing to the off-chip world.

# 6.2.2 EXECUTION OF PROGRAMS FROM INTERNAL CODE MEMORY

When code is executed in internal access mode ( $\overline{EA} = 1$ ), the opcodes are fetched from the on-chip OTP. The OTP is a self timed block which delivers data at maximum speed. This is the preferred operating mode of the PCA5007.

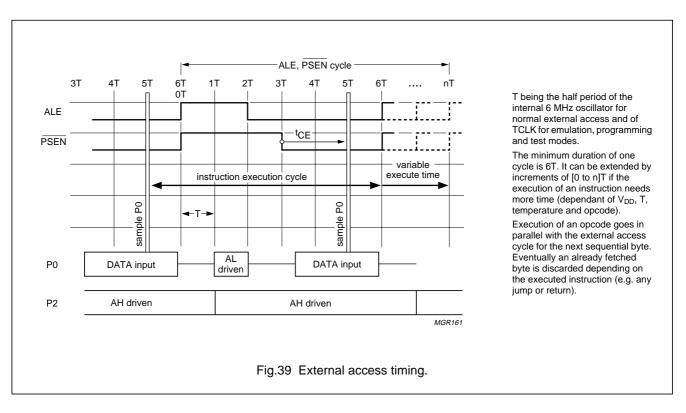

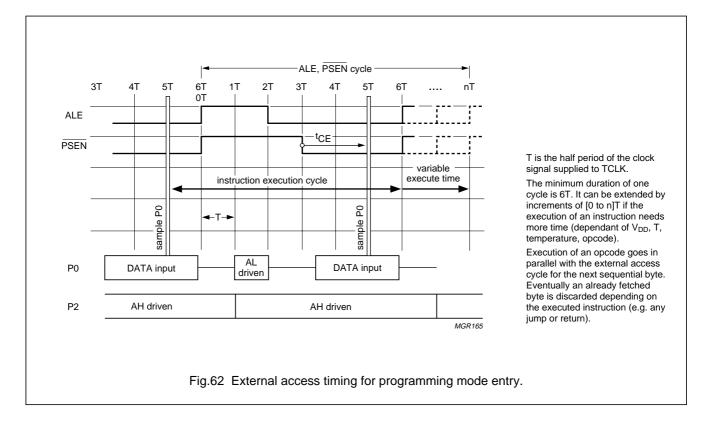

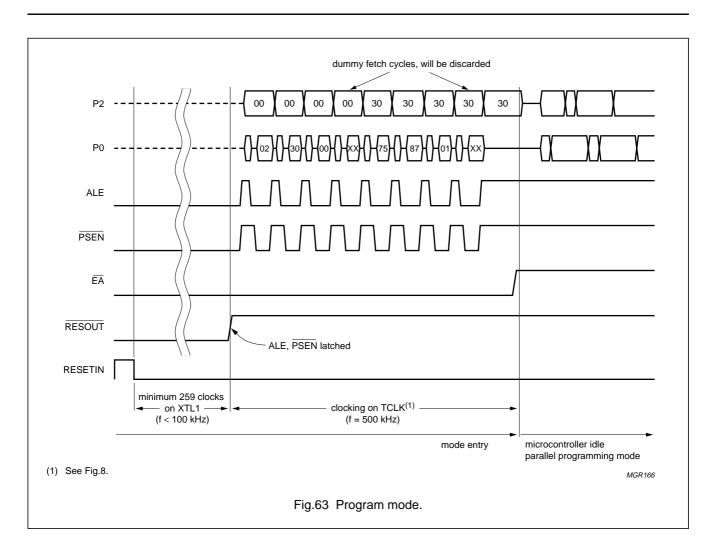

# 6.2.3 EXECUTION OF PROGRAMS FROM EXTERNAL CODE MEMORY

When code is executed in external access mode ( $\overline{EA} = 0$ ), the opcodes are fetched from an off-chip memory using the standard signals ALE,  $\overline{PSEN}$  and P0, P2 for multiplexed data and address information. In this mode the identical hardware configurations as for a standard 80C51 system can be used, even if the timing for ALE and  $\overline{PSEN}$  is slightly different because it is generated from an internal oscillator.

PCA5007

### 6.3 Overview on the different clocks used within the PCA5007

Figure 3 gives an overview on the clocks available within the PCA5007 for the different functions.

# PCA5007

### 6.4 Memory organization

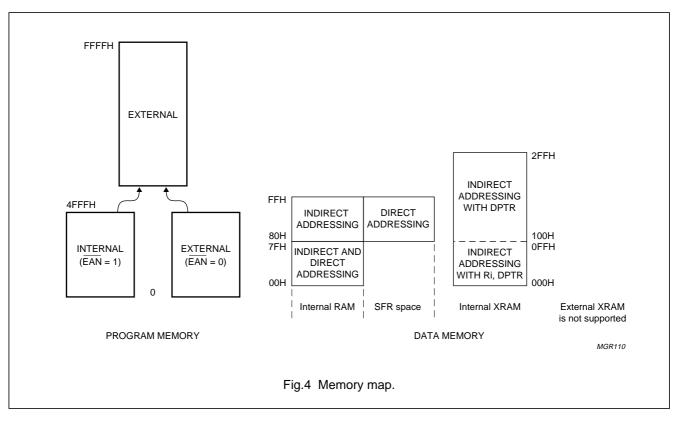

The PCA5007 has a program memory (OTP) plus data memory (RAM) on-chip. The device has separate address spaces for program and data memory (see Fig.4). If ports P0 and P2 are not used as I/O signals these pins can be used to address up to 64 kbytes of external program memory. In this case, the CPU generates the latch signal (ALE) for an external address latch and the read strobe (PSEN) for external program memory. External data memory is not supported.

### 6.4.1 PROGRAM MEMORY

After reset the CPU begins execution of the program memory at location 0000H. The program memory can be implemented in either internal OTP or external memory. If the  $\overline{EA}$  pin is strapped to V<sub>DD</sub>, then program memory fetches are directed to the internal program memory. If the  $\overline{EA}$  pin is strapped to V<sub>SS</sub>, then program memory fetches are directed to external memory.

Programming the on-chip OTP is detailed in Chapter 15. Usually Philips will deliver programmed parts to a customer. Supply of blank engineering samples is possible, but then Philips cannot give any guarantee on the programmability and retention of the program memory.

### 6.4.2 DATA MEMORY

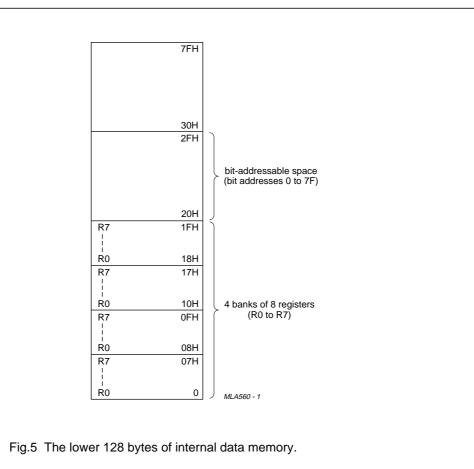

The PCA5007 contains 1024 bytes of internal RAM (consisting of 256 bytes standard RAM and 768 bytes AUX-RAM) and Special Function Registers (SFRs). Figure 4 shows the internal data memory space divided into the lower 128 bytes the upper 128 bytes and the SFR space and 768 bytes auxiliary RAM. Internal RAM locations 0 to 127 are directly and indirectly addressable. Internal RAM locations 128 to 255 are only indirectly addressable. The SFR locations 128 to 255 are only directly addressable and the auxiliary RAM is indirectly addressable as external RAM (MOVX). External Data Memory (EDM) is not supported.

### 6.4.3 SPECIAL FUNCTION REGISTERS

The second 128 bytes are the address locations of the special function registers. Table 1 shows the special function registers space. The SFRs include the port latches, timers, peripheral control, serial I/O registers, etc. These registers can only be accessed by direct addressing. There are 128 bit addressable locations in the SFR address space (those SFRs whose addresses are divisible by eight).

# PCA5007

### 6.5 Addressing

The PCA5007 has five methods for addressing source operands:

- Register

- Direct

- Register-Indirect

- Immediate

- Base-Register plus Index-Register-Indirect.

The first three methods can be used for addressing destination operands. Most instructions have a 'destination/source' field that specifies the data type, addressing methods and operands involved. For operations other than MOVs, the destination operand is also a source operand.

Access to memory addressing is as follows:

- Registers in one of the four 8-register banks through Register-Direct or Register-Indirect

- Maximum 1024 bytes of internal data RAM through Direct or Register-Indirect

- Bytes 0 to 127 of internal RAM may be addressed directly/indirectly. Bytes 128 to 255 of internal RAM share their address location with the SFRs and so may only be addressed Register-Indirect as data RAM.

- Bytes 0 to 768 of AUX-RAM can only be addressed indirectly via MOVX. Bytes 256 to 768 can only be addressed using indirect addressing with the data pointer, while bytes 0 to 255 may be also addressed using R0 or R1.

- Special function registers through Direct

- Program memory Look-Up Tables (LUTs) through Base-Register plus Index-Register-Indirect.

The PCA5007 is classified as an 8-bit device since the internal ROM, RAM, Special Function Registers (SFRs), Arithmetic Logic Unit (ALU) and external data bus are all 8 bits wide. It performs operations on bit, nibble, byte and double-byte data types.

Facilities are available for byte transfer, logic and integer arithmetic operations. Data transfer, logic and conditional branch operations can be performed directly on Boolean variables to provide excellent bit handling.

While the PCA5007 is executing code from the internal memory, ALE and  $\overrightarrow{\text{PSEN}}$  pins are inactive with ALE = LOW and  $\overrightarrow{\text{PSEN}}$  = HIGH.

External XRAM is not supported for this device, since P3.7 ( $\overline{RD}$ ) and P3.6 ( $\overline{WR}$ ) pins are not available. If the external XRAM is accessed accidentally, no  $\overline{PSEN}$  or ALE cycle is done and actual P0 values are read. Internal XRAM access is not visible from outside the chip (no ALE,  $\overline{PSEN}$ , P0 and P2 activity).

| ADDR<br>(HEX)         NAME         7         6         5         4         3         2         1         0         R/W         RESET<br>VALUE         COMM           80         P0         -         -         -         -         R/W         9FH         bit address           81         SP         -         -         -         -         R/W         9FH         bit address           81         SP         -         -         -         -         R/W         00H         -           82         DPL         -         -         -         -         R/W         00H         -           83         DPH         -         -         -         GF1         GF0         PD         IDL         R/W         00H           83         TCON         TF1         TR1         TF0         TR0         IE1         IT1         IE0         IT0         R/W         00H         bit address           89         TMOD         GATE         C/T         M1         M0         GATE         C/T         M1         M0         R/W         00H         set address           89         TMOD         GATE         C/T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | sable |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 81         SP            R/W         07H           82         DPL            R/W         00H           83         DPH           GF1         GF0         PD         IDL         R/W         00H           87         PCON         SMOD         XRE         ENIS          GF1         GF0         PD         IDL         R/W         00H           88         TCON         TF1         TR1         TF0         TR0         IE1         IT1         IE0         IT0         R/W         00H           89         TMOD         GATE         C/T         M1         M0         GATE         C/T         M1         M0         R/W         00H           84         TL0           IT1         M0         R/W         00H         IIII         IIII         M0         R/W         00H         IIIII         IIIII         IIIIII         IIIIIII         IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | sable |

| 82         DPL         Image: second s |       |

| 83         DPH         Image: style s |       |

| 87         PCON         SMOD         XRE         ENIS         -         GF1         GF0         PD         IDL         R/W         00H           88         TCON         TF1         TR1         TF0         TR0         IE1         IT1         IE0         IT0         R/W         00H         bit address           89         TMOD         GATE         C/T         M1         M0         GATE         C/T         M1         M0         R/W         00H         bit address           84         TL0         GATE         C/T         M1         M0         GATE         C/T         M1         M0         R/W         00H         GATE         GATE         C/T         M1         M0         R/W         00H         GATE         GATE         GATE         GATE         GATE         C/T         M1         M0         R/W         00H         GATE         GATE         C/T         M1         M0         R/W         00H         GATE         GATE         C/T         M1         M0         GATE         C/T         M1         M0         R/W         00H         GATE         GATE         GATE         C/T         M1         M0         GATE         C/T <td< td=""><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| 88         TCON         TF1         TR1         TF0         TR0         IE1         IT1         IE0         IT0         R/W         00H         bit address           89         TMOD         GATE         C/T         M1         M0         GATE         C/T         M1         M0         R/W         00H         bit address           8A         TL0         GATE         C/T         M1         M0         GATE         C/T         M1         M0         R/W         00H         Interval           8B         TL1         Image: Comparison of the text of t                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| 89         TMOD         GATE         C/T         M1         M0         GATE         C/T         M1         M0         R/W         00H           8A         TL0              R/W         00H           8B         TL1               R/W         00H           8C         TH0               R/W         00H           8D         TH1               R/W         00H           90         P1               R/W         00H           92         TGCON         ENB         CLK2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| 8A         TL0         Image: Constraint of the state o | sable |

| 8B         TL1         Image: Constraint of the state o | sable |

| 8C         TH0         R/W         00H           8D         TH1         Image: Constraint of the standard s                                                      | sable |

| 8D         TH1         Image: Constraint of the state o | sable |

| 90         P1         R/W         FFH         bit address           92         TGCON         ENB         CLK2         -         -         -         -         R/W         FFH         bit address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | sable |

| 92 TGCON ENB CLK2 – – – – – – R/W 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | sable |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| 93 TG0 R/W 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| 94 WUCON RUN WUP TEST CPL Z1 Z0 LOAD SET R/W 00H note 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| 95 WUC0 R/W 00H note 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 96 WUC1 R/W 00H note 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 98 S0CON SM0 SM1 - REN TB8 RB8 TI RI R/W 00H bit addres                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | sable |

| 99 S0BUF R/W 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| 9E AFCON ENB - AFC5 AFC4 AFC3 AFC2 AFC1 AFC0 R/W 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| A0 P2 R/W FFH bit addres                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | sable |

| A5 WDCON COND WD3 WD2 WD1 WD0 LD R/W 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

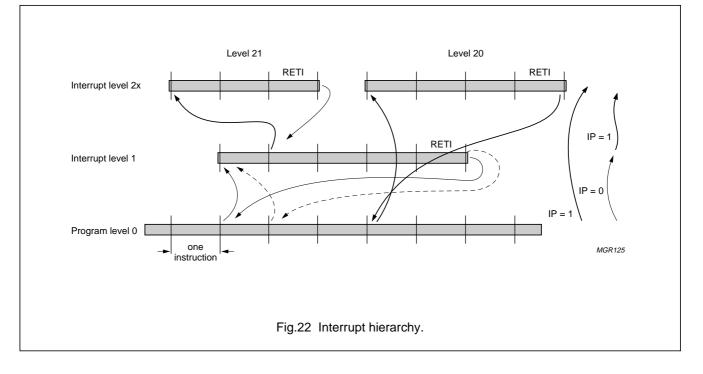

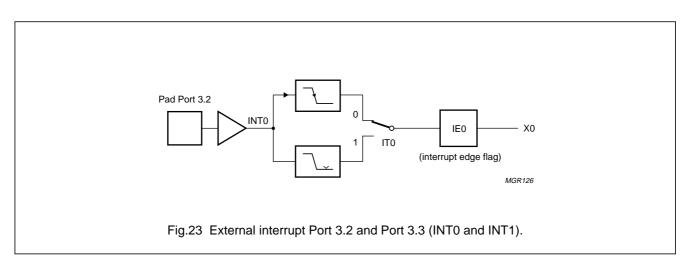

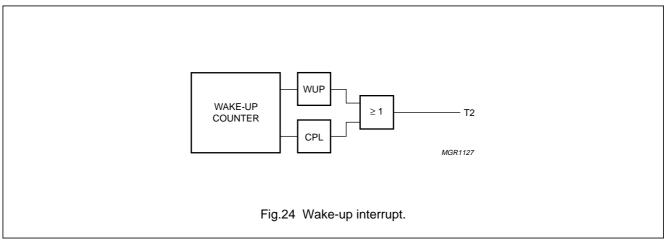

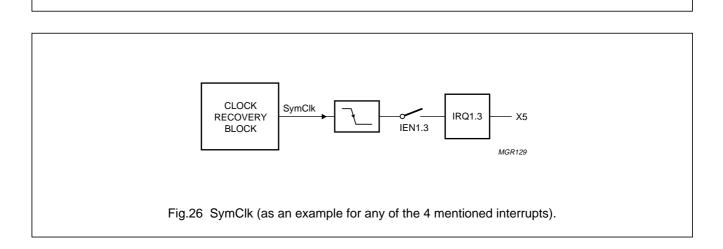

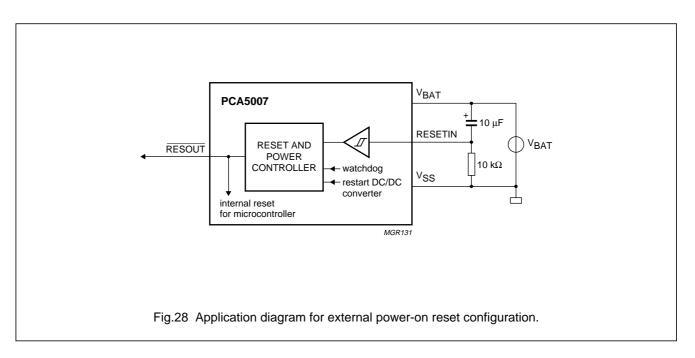

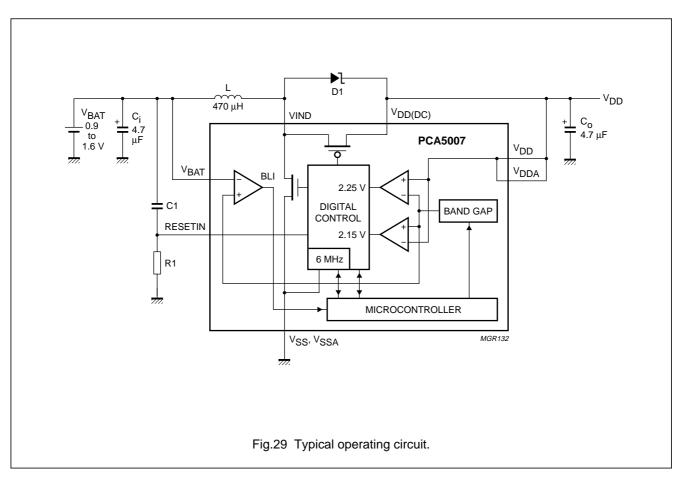

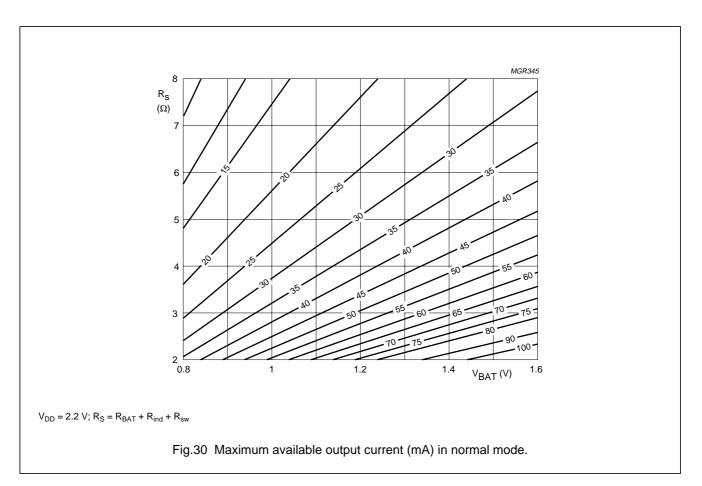

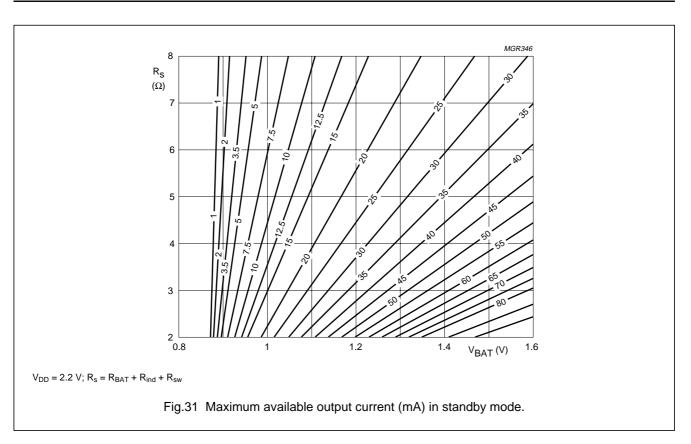

| A8 IEN0/IE EA EWU ES1 ES0 ET1 EX1 ET0 EX0 R/W 00H bit addres                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | sable |